1. What is PI (Power Integrity?)

① Power Integrity는 전원 무결성 이라고 표현합니다.

② 전원이 얼마나 Noise없이 깨끗하게 전달되는가를 말합니다.

- 일반적인 회로에서 전원 (VRM)은 PMIC or VR로 전달합니다.

- Load단 (ex, CHIP or BGA PKG Ball 등)에서 느껴지는 전원이 Noise없이 깨끗하게 전달될 수록 시스템의 오동작을 방지할 수 있습니다.

즉, PI라는 것은 Power Net에 섞여있는 Noise를 잘 분리하여 깨끗한 전원을 만들어 내는 것이라고 할 수 있습니다.

일반적인 Noise는 Decoupling Capacitor의 특성을 활용하여 High / Low Freq. 영역의 Noise로 분리할 수 있으며 우리가 흔히 보는 PCB Board에서는 100Mhz Under 수준의 노이즈를 잡아낼 수 있습니다.

-> Decoupling Capacitor 특성?

https://jasmine46.tistory.com/9

[회로이론/전자회로/수동부품] 캐패시터 / Capacitor / Decap

1. 캐패시터 (Capacitor) 두 도체 사이에 유전체를 넣어, 전하를 축적한 소자이다. ▷ 쉽게 말해서, 건전지..라고 보면 된다. 캐패시터는 Set-Level Board 설계에서 일반적으로 PI를 좋게 하기 위해서 사용

jasmine46.tistory.com

2. What is Noise Source?

- PMIC or VR (Voltage Regulator)의 Switching Noise 등

- Load (PKG, Chip)의 Dynamic Current (L∗di/dt)에 의한 Voltage Fluctuation

- Parasitic Inductance of PDN

Low Freq. Noise는 주로 PMIC or VR (Voltage Regulator)에서 발생되는 Swiching Frequency로 볼 수 있을 것이며, High Freq. Noise는 PKG 내부의 BGA Ball or Bump단에서 발생되는 Freq.로 볼 수 있습니다.

PI는 CHIP이 올바른 동작을 하기 위한 깨끗한 Power를 전달하는 것이 목적이라고 볼 수 있습니다.

깨끗한 Power를 전달하기 위해서는 PDN(Power Distribution Network)을 잘 설계하여야 하며, 유발되는 노이즈원의 Freq. 잘 캐치하여 Board 단에서 적절한 Decoupling Capacitor를 사용하여야 합니다.

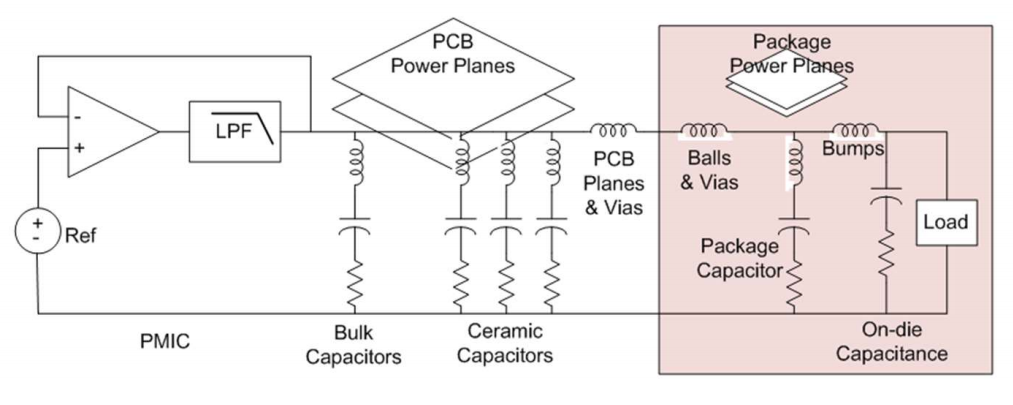

PMIC의 뒷단의 LPF는 Low pass filter를 의미하며, 일반적인 Switching 동작을 하여 일정한 전원을 만들어내기 위해서 LC 필터를 사용해야 합니다.

위에서 이야기 하였던, Board단은 위 그림에서, PMIC ~ PCB Power Planes ~ Package Ball까지 이며, 보통 50uF~100nF 등의 Bulk / Decoupling Capacitor를 사용하여 Noise를 분리하도록 합니다.

3. SSN (Simultaneous Switch Noise) | SSO (Simultaneous Switch Output)?

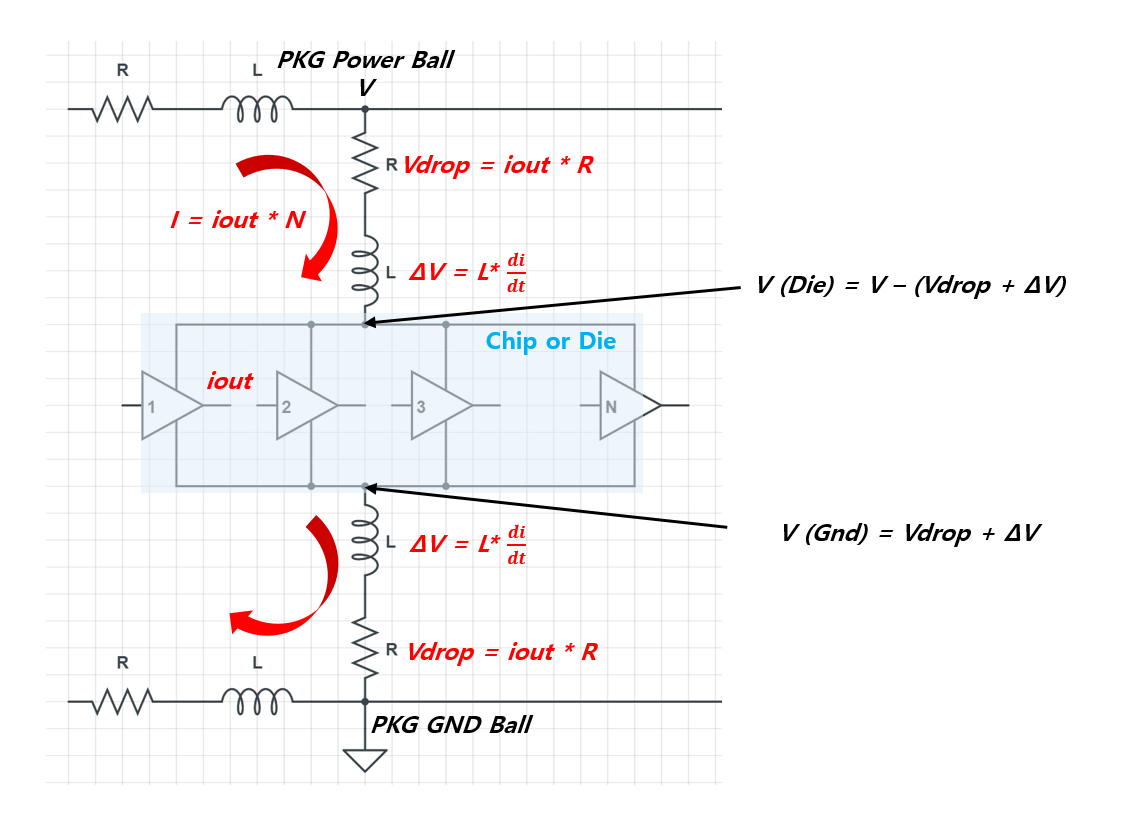

PKG 내부의 Die 혹은 Chip이 동작을 할때, CMOS들이 동시다발적으로 스위칭을 하며 전류를 끌어갑니다.

CMOS들을 제어하는 신호성분이 높은 주파수 (속도 ↑)로 동작하면서, PKG 바깥의 PCB에서 전류를 원활하게 공급을 해주어야합니다. 하지만 PCB에는 기생적으로 존재하는 인덕턴스 혹은 저항 성분으로 인하여 PKG 내부에서 필요로 하는 높은 속도로 움직이는 전류 성분에 대응을 할 수가 없습니다.

내부의 CMOS들이 동시에 Turn-On / Off 될 때 순간적으로 많은 전하를 필요로 하게 되며, 이때 전류가 원활하게 공급이 되지 않아 이로 인해 순간적으로 전압이 떨어지고 공급이 되면 올라가는 현상이 나타납니다.

이러한 전압의 떨림, 즉 이 노이즈를 의미하는 것이 SSN이라고 할 수 있습니다. (SSN = △V + Vdrop)

SSO는 이러한 SSN에 의해서 발생되는 CMOS 출력 노이즈라고 이해할 수 있습니다.

CMOS 노이즈들은 단순히 Power Ball에도 노이즈를 일으키지만, GND Plance에도 이러한 스위칭 노이즈를 일으키기 때문에 시스템의 오동작을 만들어낼 수 있습니다.

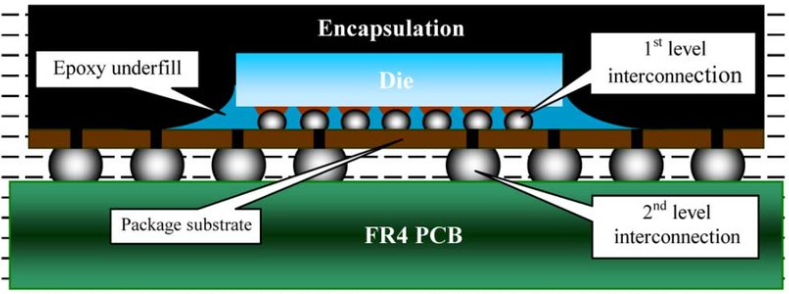

PCB에서는 BGA PKG Ball을 통하여 Power를 공급을 하게되는데, 이러한 볼 성분과 Power Plane, Gnd Plane은 모두 기생 인덕턴스 (L)를 가지고 있기 때문에 이러한 노이즈가 발생하게 됩니다.

V(t) = L * di/dt

전압 노이즈는 기생 L값이 작더라도, 내부의 Current 변화 속도(Slew)가 빠르거나 or 전류량이 클수록 크게 발생하게 됩니다. PKG 내부의 Die Current는 빠른 성분으로 움직이는 전류이기 때문에 기생 인덕턴스를 줄이는 것이 매우 필요합니다.

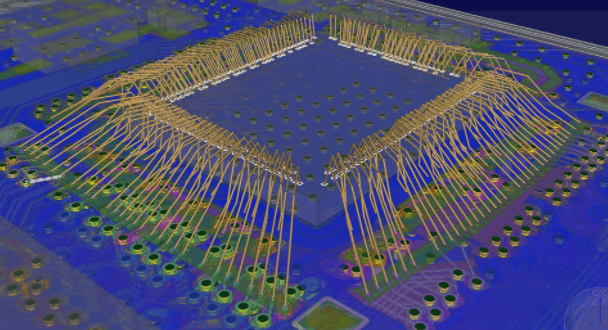

위의 그림에서는 PKG 내부에서 Bump Ball로 직접적으로 연결되는 경우도 있겠지지만, 아래 그림처럼 Wire Bonding을 통하여 연결될 수도 있습니다. Power Ball 입장에서 봤을 때, 이러한 Wire bonding들은 전부 R or L로 보이기 때문에, 주변에 Wire bonding이 여러개일 경우 저항 혹은 인덕터가 병렬로 보이므로 값이 작아지게 됩니다. 또한 Z = jωL이므로, 고주파에서는 L값이 더욱 커지므로, 이러한 인덕턴스 값을 줄이는 것이 시스템의 오동작을 방지하는데 있어 중요한 요소라고 볼 수 있습니다.

PKG 내부에 Decoupling Capacitor를 배치하는 것은 전류의 흐름을 원활하게 동작하게 하고, IC 주변에 배치하여 Loop Inductance를 줄이는 역할을 하게 됩니다. 이때 Decap의 크기는 SRF를 잘 확인하여 내부의 노이즈에 잘 대응할 수 있는 Decap을 선정하여야 하며, 충분한 전하를 공급할 수 있는 크기를 선택하여야 합니다.

https://jasmine46.tistory.com/9

[회로이론/전자회로/수동부품] 캐패시터 / Capacitor / Decap

1. 캐패시터 (Capacitor) 두 도체 사이에 유전체를 넣어, 전하를 축적한 소자이다. ▷ 쉽게 말해서, 건전지..라고 보면 된다. 캐패시터는 Set-Level Board 설계에서 일반적으로 PI를 좋게 하기 위해서 사용

jasmine46.tistory.com

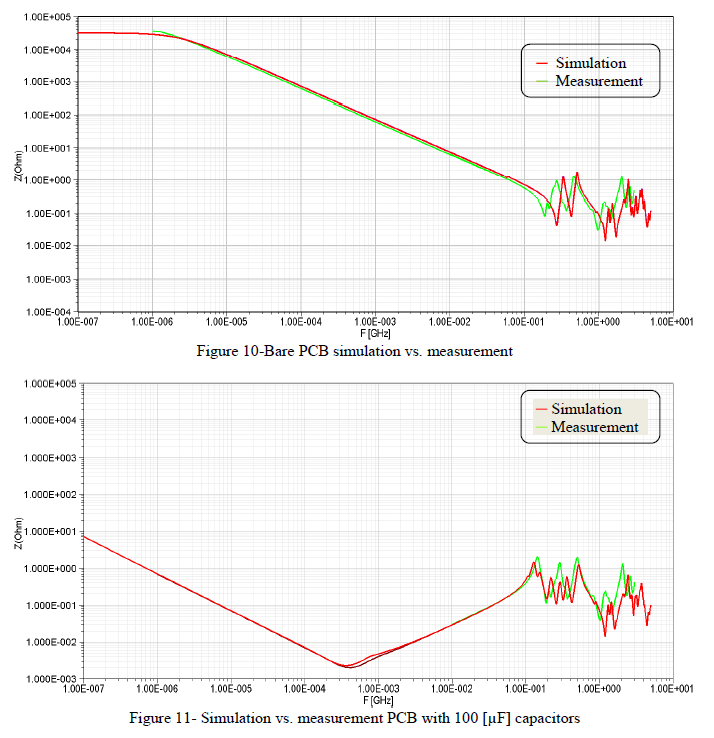

PCB Bare PDN에서 100uF Bulk Capacitor를 달았을 경우, 1Mhz Under의 임피던스 매우 낮아지면서 Low Freq. 영역에서 안정된 Power를 공급할 수 있을 것입니다. 이렇게 High Freq 영역으로 올려가며 적절한 Decap을 배치하면서 PDN |Z| 를 줄이는 것이 필요하다는 것을 알 수 있습니다.

PI 즉, Power Intergrity에 대해서 알아보았습니다.

기본적인 지식을 공부하는데 있어, 많은 도움이 되었기를 바랍니다.

오늘도 항상 수고하세요~!

오늘도 항상 즐거운 하루 되세요~!

'스터디 공간' 카테고리의 다른 글

| [Python-백준 10026] DFS - 적록색약 (0) | 2022.11.15 |

|---|---|

| [Python-백준 4963] DFS - 섬의 개수 (0) | 2022.11.15 |

| [전자회로] 부트스트랩 (Bootstrap) 회로 (0) | 2022.11.01 |

| [Google Colab Pro Plus] 구글 코랩 프로 플러스 사용 후기 / 데이터 사이언스 공부 하기 / 머신러닝 (0) | 2022.10.27 |

| [Python] 고위함수(higher-order function) map(), filter(), lambda() / namedtuple 사용하기 (0) | 2022.06.24 |

댓글